# Cellron Datasheet

Version 1.1 Teleron Copyright©2022

# **About This Document**

This document provides the specifications for the Cellron development board module.

# **Documentation Change Notification**

Provides email notifications to keep customers updated on changes to technical documentation. Please subscribe at <u>www.teleron.oguzkagansavunma.com</u> subscribe address.

# CONTENTS

**1** Overview

## 2 Pin Definitions

- 2.1 Pin Layout

- 2.2 Pin Description

#### **3** Functional Description

- 3.1 CPU and Internal Memory

- 3.2 External Flash and SRAM

- 3.3 Crystal Oscillators

- 3.4 RTC and Low Power Management

#### 4 Peripherals and Sensors

#### **5** Electrical Characteristics

- 5.1 Absolute Maximum Values

- 5.2 Recommended Operating Conditions

- 5.3 DC Characteristics (3.3 V, 25 °C)

#### 6 Physical Dimension

# **List of Tables**

| 1. Cellron Specifications            | 1 |

|--------------------------------------|---|

| 2. Pin Definitions                   | 2 |

| 3. Absolute Maximum Values           | 6 |

| 4. Recommended Operating Conditions  | 6 |

| 5. DC characteristics (3.3 V, 25 °C) | 6 |

# **List of Figures**

| 1. Cellr | on Pin Layout (Top View)   | 2 |

|----------|----------------------------|---|

| 2. Phys  | ical Dimensions of Cellron | 8 |

2. Physical Dimensions of Cellron

# 1. Overview

Cellron is a powerful general Wi-Fi+BT+LTE MCU module targeting a wide range of applications, from low-power sensor networks to the most demanding tasks such as audio encoding, music streaming and MP3 decoding.

At the center of this module is the ESP32-Wroom chip. The embedded chip is designed to be scalable and adaptable. There are two CPU cores that can be controlled separately, and the CPU clock frequency is adjustable from 80 MHz to 240 MHz. The user can also turn off the CPU and The chip also has a low-power coprocessor that can be used instead of the CPU to save power while performing tasks that do not require much computing power, such as monitoring of peripherals. ESP32 integrates a rich set of peripherals such as capacitive touch sensors, Hall sensors, SD card interface, Ethernet, high speed SPI, UART, I2S and I2C.

The integration of Bluetooth, Bluetooth LE, Wi-Fi and 4G-LTE ensures that a wide range of applications can be targeted, and that the module is all-around: using Wi-Fi allows a large physical range and direct connection to the Internet through a Wi-Fi or 4G-LTE module. Wi-Fi or 4G-LTE module, while using Bluetooth, allows the user to conveniently connect to the phone or broadcast low energy beacons for detection. The sleep current of the ESP32 chip is less than 5  $\mu$ A, making it suitable for battery-powered and wearable electronics applications. The module supports up to 150 Mbps data rate and 20 dBm output power at antenna to provide the widest physical range. Therefore, the module offers industry-leading features and the best performance for electronic integration, range, power consumption and connectivity.

Table 1 provides the specifications of Cellron .

| Categories | Items                                        | Specifications                                                                                                           |

|------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

|            |                                              | 802.11 b/g/n (802.11n up to 150 Mbps)                                                                                    |

| Wi-Fi      | Protocols                                    | A-MPDU and A-MSDU aggregation and 0.4 µs guard interval support                                                          |

|            | Frequency range                              | 2.4 GHz ~2.5 GHz                                                                                                         |

|            | Protocols                                    | Bluetooth v4.2 BR/EDR and Bluetooth LE specification                                                                     |

|            |                                              | NZIF receiver with –97 dBm sensitivity                                                                                   |

| Bluetooth  | Radio                                        | Class-1, class-2 and class-3 transmitter                                                                                 |

|            | Module interfaces                            | SD card, UART, SPI, SDIO, I2C, LED PWM, Motor PWM,<br>I2S, IR, pulse counter, GPIO, capacitive touch sensor, ADC,<br>DAC |

| Hardware   | On-chip Sensor                               | Hall sensor                                                                                                              |

| Taluwale   | Integrated crystal                           | 40 MHz crystal                                                                                                           |

|            | Integrated SPI flash                         | 4 MB                                                                                                                     |

|            | Operating voltage/<br>Power supply           | 2.7 V ~ 3.6 V                                                                                                            |

|            | Operating current                            | Average: 80 mA                                                                                                           |

|            | Minimum current delivered<br>by power supply | 500 mA                                                                                                                   |

|            | Recommended Operating<br>Temperature Range   | -40 °C ~+85 °C                                                                                                           |

|            | Package size                                 | $(18.00\pm0.10) \text{ mm} \times (25.50\pm0.10) \text{ mm} \times (3.10\pm0.10) \text{ mm}$                             |

Table 1: Cellron Specifications

# 2. Pin Definitions

# 2.1 Pin Layout

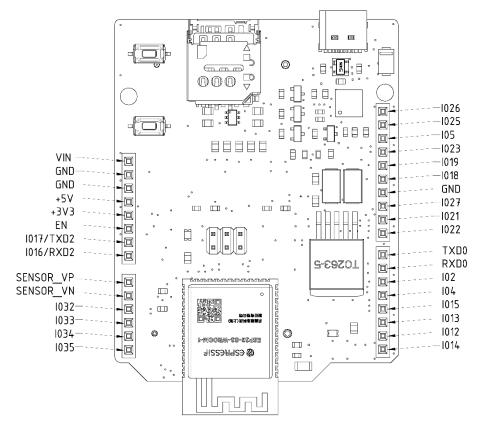

Figure 1: Cellron Pin Layout (Top View)

## 2.2 Pin Description

Cellron has 38 pins. See pin definitions in Table 2.

#### Table 2: Pin Definitions

| Name              | No.   | Туре | Function                                                            |  |

|-------------------|-------|------|---------------------------------------------------------------------|--|

| GND               | 1     | Р    | Ground                                                              |  |

| 3V3               | 2     | Р    | Power supply                                                        |  |

| EN                | 3     | Ι    | Module-enable signal. Active high.                                  |  |

| SENSOR_VP         | 4     | Ι    | GPIO36, ADC1_CH0, RTC_GPIO0                                         |  |

| SENSOR_VN         | 5     | Ι    | PIO39, ADC1_CH3, RTC_GPIO3                                          |  |

| IO34              | 6     | Ι    | GPIO34, ADC1_CH6, RTC_GPIO4                                         |  |

| IO35              | 7     | Ι    | GPIO35, ADC1_CH7, RTC_GPIO5                                         |  |

| IO32              | 8     | I/O  | GPIO32, XTAL_32K_P (32.768 kHz crystal oscillator input), ADC1_CH4, |  |

| 1032              | 8 1/0 |      | TOUCH9, RTC_GPIO9                                                   |  |

| IO33 9 <b>I/O</b> |       | I/O  | GPIO33,XTAL_32K_N(32.768kHzcrystaloscillatoroutput),ADC1_CH5,       |  |

| 1055              | ,     | 1/0  | TOUCH8, RTC_GPIO8                                                   |  |

| İsim     | No. | Tip | Fonksiyon                                                   |

|----------|-----|-----|-------------------------------------------------------------|

| IO25     | 10  | I/O | GPIO25, DAC_1, ADC2_CH8, RTC_GPIO6, EMAC_RXD0               |

| IO26     | 11  | I/O | GPIO26, DAC 2, ADC2 CH9, RTC GPIO7, EMAC RXD1               |

| IO27     | 12  | I/O | GPIO27, ADC2_CH7, TOUCH7, RTC_GPIO17, EMAC_RX_DV            |

| IO14     | 13  | I/O | GPIO14,ADC2_CH6,TOUCH6,RTC_GPIO16,MTMS,HSPICLK,<br>HS2_CLK, |

|          |     |     | SD_CLK, EMAC_TXD2                                           |

| IO12     | 14  | I/O | GPIO12,ADC2_CH5,TOUCH5,RTC_GPIO15,MTDI,HSPIQ,<br>HS2_DATA2, |

|          |     |     | SD_DATA2, EMAC_TXD3                                         |

| GND      | 15  | Р   | Ground                                                      |

| IO13     | 16  | I/O | GPIO13,ADC2_CH4,TOUCH4,RTC_GPIO14,MTCK,HSPID,<br>HS2_DATA3, |

|          |     |     | SD_DATA3, EMAC_RX_ER                                        |

| SHD/SD2* | 17  | I/O | GPIO9, SD_DATA2, SPIHD, HS1_DATA2, U1RXD                    |

| SWP/SD3* | 18  | I/O | GPIO10, SD_DATA3, SPIWP, HS1_DATA3, U1TXD                   |

| SCS/CMD* | 19  | I/O | GPIO11, SD_CMD, SPICS0, HS1_CMD, U1RTS                      |

| SCK/CLK* | 20  | I/O | GPIO6, SD_CLK, SPICLK, HS1_CLK, U1CTS                       |

| SDO/SD0* | 21  | I/O | GPIO7, SD_DATA0, SPIQ, HS1_DATA0, U2RTS                     |

| SDI/SD1* | 22  | I/O | GPIO8, SD_DATA1, SPID, HS1_DATA1, U2CTS                     |

| IO15     | 23  | I/O | GPIO15,ADC2_CH3,TOUCH3,MTDO,HSPICS0,RTC_GPIO13,<br>HS2_CMD, |

|          |     |     | SD_CMD, EMAC_RXD3                                           |

| IO2      | 24  | I/O | GPIO2, ADC2_CH2, TOUCH2, RTC_GPIO12, HSPIWP, HS2_DATA0,     |

|          |     |     | SD_DATA0                                                    |

| IO0      | 25  | I/O | GPIO0, ADC2_CH1, TOUCH1, RTC_GPIO11, CLK_OUT1, EMAC_TX_CLK  |

| IO4      | 26  | I/O | GPIO4, ADC2_CH0, TOUCH0, RTC_GPIO10, HSPIHD, HS2_DATA1,     |

|          |     |     | SD_DATA1, EMAC_TX_ER                                        |

| IO16     | 27  | I/O | GPIO16, HS1_DATA4, U2RXD, EMAC_CLK_OUT                      |

| IO17     | 28  | I/O | GPIO17, HS1_DATA5, U2TXD, EMAC_CLK_OUT_180                  |

| IO5      | 29  | I/O | GPIO5, VSPICS0, HS1_DATA6, EMAC_RX_CLK                      |

| IO18     | 30  | I/O | GPIO18, VSPICLK, HS1_DATA7                                  |

| IO19     | 31  | I/O | GPIO19, VSPIQ, U0CTS, EMAC TXD0                             |

| NC       | 32  | -   | -                                                           |

| IO21     | 33  | I/O | GPIO21, VSPIHD, EMAC TX EN                                  |

| RXD0     | 34  | I/O | GPIO3, U0RXD, CLK OUT2                                      |

| TXD0     | 35  | I/O | GPIO1, U0TXD, CLK OUT3, EMAC RXD2                           |

| IO22     | 36  | I/O | GPIO22, VSPIWP, U0RTS, EMAC TXD1                            |

| IO23     | 37  | I/O | GPIO23, VSPID, HS1_STROBE                                   |

| GND      | 38  | Р   | Ground                                                      |

#### NOTE:

• Pins SCK/CLK, SDO/SD0, SDI/SD1, SHD/SD2, SWP/SD3 and SCS/CMD, namely GPIO6 to GPIO11, are connected to the integrated SPI flash integrated on the module and are not recommended for other uses.

# **3. Functional Description**

This section describes the modules and functions integrated into the Cellron board.

## **3.1 CPU and Internal Memory**

The Cellron board contains one low power esp32 wroom 32 microprocessor. Internal memory includes:

- 448 KB ROM for booting and core functions.

- 520 KB of on-chip SRAM for data and instructions.

- 8 KB of SRAM in RTC, which is called RTC FAST Memory and can be used for data storage; Accessed by the main CPU during RTC Boot from Deep-sleep mode.

- The 8 KB of SRAM in RTC, which is called RTC SLOW Memory and can be accessed by the coprocessor during the Deep-sleep mode.

- 1 Kbit of eFuse: 256 bits are used for the system and the remaining 768 bits are reserved for customer applications, including flash encryption and chip ID.

## 3.2 External Flash and SRAM

ESP32 supports multiple external QSPI flash and SRAM chips. ESP32 also supports hardware encryption/decryption based on AES to protect developers' programs and data in flash.

ESP32 can access the external QSPI flash and SRAM via high speed caches.

- The external flash can be mapped into CPU instruction memory space and read-only memory space at the same time.

- When external flash is mapped into CPU instruction memory space, up to 11 MB + 248 KB can be mapped at a time. Note that if more than 3 MB + 248 KB are mapped, cache performance will be reduced due to speculative reads by the CPU.

- When external flash is mapped into read-only data memory space, up to 4 MB can be mapped at a time. 8-bit, 16-bit and 32-bit reads are supported.

- External SRAM can be mapped to the CPU data memory area. Up to 4 MB can be mapped at a time. 8-bit, 16-bit and 32-bit reads and writes are supported.

Cellron board integrates a 4MB SPI flash, which is connected to GPIO6, GPIO7, GPIO8, GPIO9, GPIO10 and GPIO11. These six pins cannot be used as regular GPIOs.

## **3.3 Crystal Oscillators**

The module uses a 40 MHz crystal oscillator.

## 3.4 RTC and Low Power Management

With the use of advanced power management technologies, Cellron can switch between different power modes.

## 4. Peripherals and Sensors

#### NOTE:

- External connections can be made to any GPIO except GPIOs in the 6 to 11 range.

- These six GPIOs are connected to the module's integrated SPI flash.

# **5. Electrical Characteristics**

## 5.1 Absolute Maximum Values

Voltages above the absolute maximum values listed in Table 3 below can cause permanent damage to the device.

| Symbol               | Parameter                     | Min  | Max   | Unit |

|----------------------|-------------------------------|------|-------|------|

| VDD                  | Power supply voltage          | -0.3 | 7.6   | V    |

| Ioutput <sup>1</sup> | Cumulative I/O output current | -    | 1,100 | mA   |

| Tstore               | Storage temperature           | -40  | 150   | °C   |

#### Table 3: Absolute Maximum Values

## **5.2 Recommended Operating Conditions**

#### **Table 4: Recommended Operating Conditions**

| Symbol | Parameter                                  | Min | Typical | Max | Unit |

|--------|--------------------------------------------|-----|---------|-----|------|

| VDD33  | Power supply voltage                       | 2.7 | 5.0     | 7.6 | V    |

| IVDD   | Current delivered by external power supply | 0.5 | -       | -   | А    |

| Т      | Operating temperature                      | -40 | -       | 85  | °C   |

# 5.3 DC Characteristics (3.3 V, 25 °C)

#### Table 5: DC characteristics (3.3 V, 25 °C)

| Symbol         | Parameter                 | Min                                   | Тур                 | Max | Unit               |    |

|----------------|---------------------------|---------------------------------------|---------------------|-----|--------------------|----|

| CIN            | Pin capacitance           |                                       | -                   | 2   | -                  | pF |

| VIH            | High-level input voltage  |                                       | $0.75 \times VDD^1$ | -   | VDD <sup>1+0</sup> | V  |

|                |                           |                                       |                     |     | .3                 |    |

| VIL            | Low-level input voltage   |                                       | -0.3                | -   | 0.25×VD            | V  |

|                |                           |                                       |                     |     | $D^1$              |    |

| H              | High-level input current  | -                                     | -                   | 50  | nA                 |    |

| IIL            | Low-level input current   |                                       | -                   | -   | 50                 | nA |

| VOH            | High-level output voltage |                                       | $0.8 \times VDD^1$  | -   | -                  | V  |

| VOL            | Low-level output voltage  |                                       | -                   | -   | 0.1×VD             | V  |

|                |                           |                                       |                     |     | $D^1$              |    |

|                |                           | VDD3P3_CPUpowerdomain <sup>1, 2</sup> | -                   | 40  | -                  | mA |

| IOH High-level | High-level source current | VDD3P3_RTCpowerdomain <sup>1, 2</sup> | -                   | 40  | -                  | mA |

|                |                           | VDD_SDIO power domain <sup>1, 3</sup> | -                   | 20  | -                  | mA |

| Symbol                                           | Parameter                                                                                                                | Min | Тур | Max | Unit |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| lOL                                              | Low-level sink current<br>(VDD <sup>1</sup> = 3.3 V, V <i>OL</i> = 0.495 V,<br>output drive strength set to the maximum) |     | 28  | -   | mA   |

| RPU                                              | Resistance of internal pull-up resistor                                                                                  | -   | 45  | -   | kΩ   |

| R <i>PD</i>                                      | Resistance of internal pull-down resistor                                                                                | -   | 45  | -   | kΩ   |

| $ \begin{matrix} V_{IL\_n} \\ RST \end{matrix} $ | Low-level input voltage of CHIP_PU to power off the chip                                                                 | -   | -   | 0.6 | V    |

#### Notes:

- 1. For VDD3P3\_CPU and VDD3P3\_RTC power domain, per-pin current sourced in the same domain is gradually reduced from around 40 mA to around 29 mA, VOH >=2.64 V, as the number of current-source pins increases.

- 2. Pins occupied by flash and/or PSRAM in the VDD\_SDIO power domain were excluded from the test.

# 6. Physical Dimensions

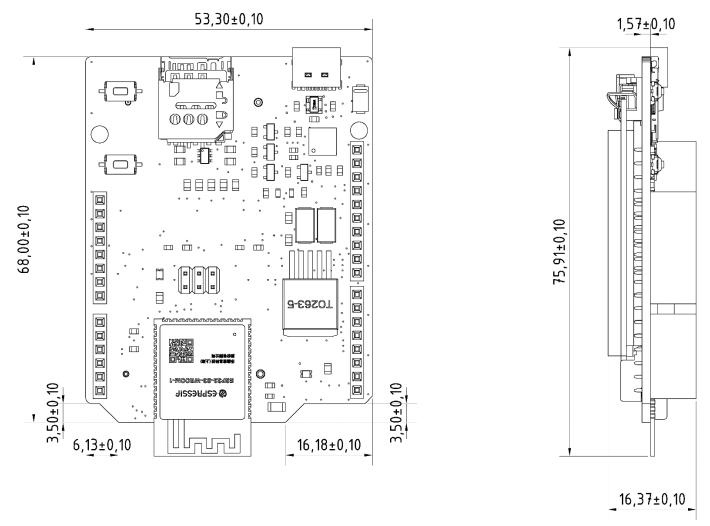

**Figure 2: Physical Dimensions of Cellron**